# VATAGP3\_1

## Specifications (preliminary) V0.94

December 2004

## Table of Contents

| General                                                         | 3                                         |

|-----------------------------------------------------------------|-------------------------------------------|

| Physical                                                        | 3                                         |

| Electrical                                                      | 4                                         |

| Pad Description                                                 | 5                                         |

| Layout                                                          | 8                                         |

| Functional description                                          | 10                                        |

| .1 Using VATAGP3_1 in parallel                                  | 10                                        |

| .2 Current compensation                                         | 11                                        |

| .3 Biasing                                                      | 12                                        |

| .4 Control register                                             | 13                                        |

| .5 ASIC test and calibration                                    | 14                                        |

| .6 Threshold DACs                                               | 14                                        |

|                                                                 |                                           |

| ) Mode 1: Serial readout                                        | 15                                        |

| .1 Mode 2: Sparse readout                                       | 16                                        |

| .2 Mode 3: Sparse readout with neighbour channels               |                                           |

| .3 Mode 4: Random Access Read-out (RAR) with neighbour channels | 20                                        |

|                                                                 | <ul> <li>2 Current compensation</li></ul> |

## 1 General

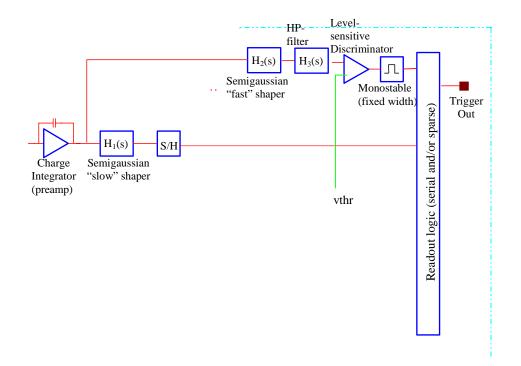

The VATAGP3\_1 is a 128-channel "general purpose" charge sensitive amplifier. Each channel features low-noise/low-power buffered preamplifiers, a shaper with sample/hold, multiplexed analogue readout and calibration facilities. In addition, each channel has a fast shaper that gives a trigger signal. The analogue value and the address of the trigging channels are read out with a flexible serial read-out (VA-style), sparse read-out system, sparse read-out with neighbours or read-out of any desired channel, the Random-Access Read-out (RAR). The VATAGP3\_1 also offers input leakage current compensation automatically adjusted in each preamplifier channel.

The VATAGP3\_1 is designed for use in systems employing many chips in parallel, sharing some control lines and all output lines with the other modules.

## 2 Physical

| Process:             | $0.8 \ \mu m$ N-well CMOS, double poly, double metal.       |                             |  |

|----------------------|-------------------------------------------------------------|-----------------------------|--|

| Die size:            | 10660 μm x 6120 μm(including scribe)<br>Thickness: ~ 600 μm |                             |  |

| Input bonding pads:  | Pad size:                                                   | 90 μm x 50 μm               |  |

|                      | Pad pitch:                                                  | 91.2 $\mu$ m (see Figure 3) |  |

| Control, output, and | Single row.                                                 |                             |  |

| biasing pads:        | Pad size:                                                   | 90 µm x 90 µm               |  |

|                      | Pad pitch:                                                  | 140 µm (see Figure 2)       |  |

| Analogue Power pads: | Pad size:                                                   | 90 µm x 200 µm              |  |

## **3 Electrical**

(Simulated values, to be verified by measurements)

| Power rails:                                                     | Each with sep  | , VSS = -2 V<br>parate connect<br>and digital sec | tions for ana                     | alogue (AVD                                               |                                                            |

|------------------------------------------------------------------|----------------|---------------------------------------------------|-----------------------------------|-----------------------------------------------------------|------------------------------------------------------------|

| Back contact:                                                    | Connect to A   | VSS (-2V)                                         |                                   |                                                           |                                                            |

| Current description:<br>(Quiescent, typical va<br>mbias=500 µA)  | lues with      | DVDD<br>DVSS<br>DGND<br>AVDD<br>AVSS<br>AGND      |                                   |                                                           | ~3 mA?<br>~6 mA?<br>0 mA<br>~50 mA?<br>~100 mA?<br>~50 mA? |

| Input bias currents:                                             |                | Nominal val                                       | ues                               |                                                           |                                                            |

| mbias                                                            |                | 500 μΑ                                            |                                   | all other bia<br>internally g<br>and can be<br>unconnecte | generated                                                  |

| Power dissipation: (T                                            | ypical values) | Quiescent:                                        | 300 mW (                          | (2.3 mW/cha                                               | nnel)??                                                    |

| Gain:<br>DNR:<br>Peaking time, slow sh<br>Peaking time, fast sha | •              | ~ 44 µA/fC<br>~ +18 fC<br>~ 4 µs<br>~ 150 ns      | fC (differential branches added). |                                                           |                                                            |

### 4 Pad Description

Bias pads which do not require bonding (internally generated or pull-up/pull-down) can be bonded for external decoupling, adjustment or forcing. Pads described clock-wise from upper left to lower left (excluding input pads). Positive current direction into the chip.

| Pad name    | Туре | Description                      | Nominal value       |

|-------------|------|----------------------------------|---------------------|

| ai0-6       | di   | Address in, single-ended digital | Current (100 µA)    |

|             |      | current signal                   |                     |

| shift_in_d  | di   | Shift-register input (downwards) | logical             |

| shift_out_u | do   | Shift-register output (upwards)  | Logical             |

| vi          | ldi  | Veto input (pos. phase)          | low v. logical (pd) |

| vib         | ldi  | Veto input (neg. phase)          | low v. logical (pu) |

| regin       | di   | Data input for control register  | logical (pd)        |

Pad-row on the ASIC top side:

Pad-row on the ASIC right side:

| Pad name  | Туре | Description                                                         | Nominal value       |

|-----------|------|---------------------------------------------------------------------|---------------------|

| AGND      | р    | Signal ground for the analogue part                                 | 0 V                 |

| DGND      | р    | Connect to AGND                                                     | 0 V                 |

| DVDD      | р    | Digital VDD                                                         | 2 V                 |

| DVSS      | р    | Digital VSS                                                         | -2 V                |

| clkin     | di   | Clock for control register                                          | Logical             |

| sh        | ldi  | Sample and hold (pos. phase)                                        | low v. logical      |

| shb       | ldi  | Sample and hold (neg. phase)                                        | low v. logical      |

| res       | ldi  | Reset of the readout logic (pos. phase)                             | low v. logical (pd) |

| resb      | ldi  | Reset of the readout logic (neg. phase)                             | low v. logical (pu) |

| shiftreg  | ldi  | Readout mode (pos. phase)                                           | low v. logical (pu) |

| shiftregb | ldi  | Readout mode (neg. phase)                                           | low v. logical (pd) |

| gckb      | ldi  | Clock for readout (neg. phase)                                      | low v. logical      |

| gck       | ldi  | Clock for readout (pos. phase)                                      | low v. logical      |

| addr0-6   | do   | Digital output of hit channel address                               | Current (100 µA)    |

| addr7-10  | do   | Digital output of chip address                                      | Current (100 µA)    |

| ioref     | ai   | Current sink for the address output buffer                          | Connect to ~0V      |

| mgo       | ao   | Multi-hit trigger output                                            | Current             |

| to        | do   | Trigger out (positive phase),<br>referred to DVDD                   | ~ -1.3 mA           |

| tob       | do   | Trigger out (negative phase),<br>referred to DVSS                   | ~ 1.3 mA            |

| vthrh     | ai   | High threshold for the discriminator                                | 2V?                 |

| vfsf      | ai   | Control voltage for the feedback resistor (NMOS) in the fast shaper | 200 mV (int. gen.)  |

| vfss    | ai | Control voltage for the feedback      | 150 mV (int. gen.)  |

|---------|----|---------------------------------------|---------------------|

|         |    | resistor (NMOS) in the slow shaper    |                     |

| vfp     | ai | Control voltage for the feedback      | -300 mV (int. gen.) |

| -       |    | resistor (NMOS) in the preamplifier   |                     |

| outm_u  | ao | Diff. analogue output, neg. phase     | 0-200 µA            |

|         |    | (upwards shift-register)              |                     |

| outp_u  | ao | Diff. analogue output, pos. phase     | 0-200 µA            |

| _       |    | (upwards shift-register)              |                     |

| outm_d  | ao | Diff. analogue output, neg. phase     | 0-200 µA            |

|         |    | (downwards shift-register)            |                     |

| outp_d  | ao | Diff. analogue output, pos. phase     | 0-200 µA            |

|         |    | (downwards shift-register)            |                     |

| vthr    | ai | Normal threshold for the              | 1 50 mV?            |

|         |    | discriminator                         |                     |

| cali    | ai | Test pulse with internal capacitor    | voltage step        |

| cale    | ai | Test pulse with external capacitor    | charge              |

| mbias   | ai | Bias reference for all the internally | 500 µA              |

|         |    | generated biases                      |                     |

| AVSS_CC | ai | Reference for current compensation    | -2V                 |

| AVDD    | р  | analogue VDD                          | 2 V                 |

| AVSS    | р  | analogue VSS                          | -2 V                |

Pad-row on the ASIC bottom side:

| Pad name    | Туре | Description                         | Nominal value    |

|-------------|------|-------------------------------------|------------------|

| regout      | do   | Data output of the control register | logical          |

| vob         | ldo  | Veto output (neg. phase)            | low v. logical   |

| vo          | ldo  | Veto output (pos. phase)            | low v. logical   |

| shift_in_u  | di   | Shift-register input (upwards)      | logical          |

| shift_out_d | do   | Shift-register output (downwards)   | logical          |

| ai6-0       | di   | Address in, single-ended digital    | Current (100 µA) |

|             |      | current signal                      |                  |

Inner control pad row, from upper to lower:

| Pad name | Туре | Description              | Nominal value     | Coordinates   |

|----------|------|--------------------------|-------------------|---------------|

| dlt      | ldi  | Inhibit further trigger  | Internally pulled | 9854 / 5061.8 |

|          |      | generation, pos. phase   | low               |               |

| dltb     | ldi  | Inhibit further trigger  | Internally pulled | 9854 / 4921.8 |

|          |      | generation, neg. phase   | high              |               |

| CS       | ldi  | Chip select (to select a | Internally pulled | 9854 / 4781.8 |

|          |      | specific chip for RAR    | low               |               |

|          |      | read-out), pos. phase    |                   |               |

| csb      | ldi  | Chip select (to select a | Internally pulled | 9854 / 4641.8 |

|          |      | specific chip for RAR    | high              |               |

|          |      | read-out), neg. phase    |                   |               |

| Pad      | Туре  | Description                                                                                                                                         | Nominal value                                                 | Coordinates   |

|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------|

| name     |       |                                                                                                                                                     |                                                               |               |

| slewb    | ai    | Bias for the slew rate limitation circuit                                                                                                           | -6 µA (int. gen.)                                             | 9877.8 / 2904 |

| obi      | ai    | Bias for the discriminators                                                                                                                         | 90 µA (int. gen.)                                             | 9877.8 / 2764 |

| mo_bi    | ai    | Bias for the address and mgo current sources.                                                                                                       | -140 µA(int.gen.)                                             | 9877.8 / 2624 |

| vref     | ao/ai | Reference for the output buffer,<br>internally generated by a dummy slow<br>shaper                                                                  | ~ -600 mV                                                     | 9877.8 / 2484 |

| trigwb   | ai    | Trigger width bias                                                                                                                                  | -12 µA (int. gen.)                                            | 9877.8 / 2344 |

| shabf    | ai    | Bias for the fast shaper                                                                                                                            | 65 µA (int. gen.)                                             | 9877.8 / 2204 |

| vrc      | ai    | Control voltage for HP -filter resistor<br>(NMOS) in front of discriminator.<br>Possible to change with the global<br>control bit <i>vrcn_sel</i> . | <i>Vrcn_sel</i> = 0:<br>1.4 V<br><i>Vrcn_sel</i> = 1:<br>1.2V | 9877.8 / 2064 |

| preb     | ai    | Bias for the preamplifiers                                                                                                                          | 500 µA (int. gen.)                                            | 9877.8 / 1924 |

| shabs    | ai    | Bias for the slow shaper                                                                                                                            | 22 µA (int. gen.)                                             | 9877.8 / 1784 |

| ibuf     | ai    | Bias for the analog output buffer                                                                                                                   | 220 µA (int. gen.)                                            | 9877.8 / 1644 |

| ref_bias | ai    | Bias for threshold DACs                                                                                                                             | 20 µA (int. gen.)                                             | 9877.8 / 1504 |

Pads on the second pad-row, listed from upper to lower. These pads are for over-riding of internally generated biases.

p = power, di = digital in, do = digital out, ldi = low voltage differential digital in,ldo = low voltage differential digital out, ai=analogue in, ao = analogue out,pu = pull-up, pd = pull-downLow voltage logical = 0V("1")/-0.2V("0")Logical = +2V("1")/-2V("0")

### 5 Layout

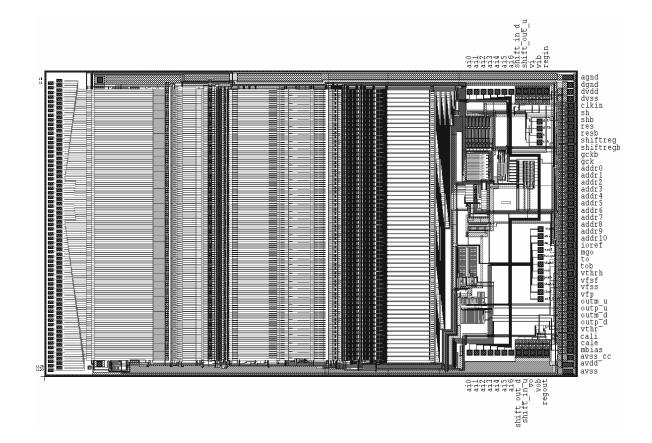

#### [dlt, dltb, cs and csb pads]

[Redundant analogue GND pads (Connect for lower GND line series resistance)]

Figure 1: Chip plot of the VaTagp3\_1

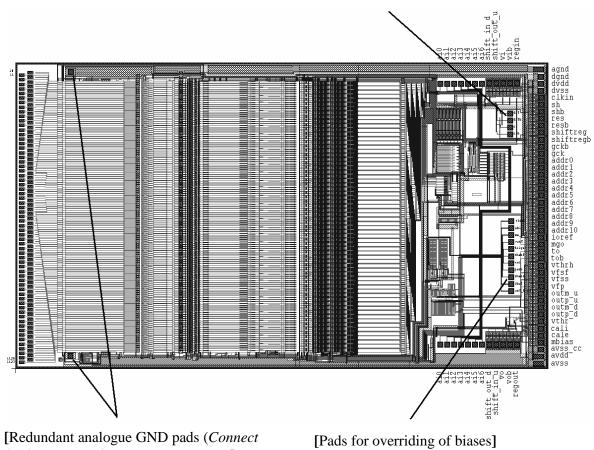

Figure 2: Chip geometry & pad placement (Not to scale - all dimensions in µm. Please note that the referred co-ordinates are layout co-ordinates. Add 50-100 µm on each side for scribe/cutting tolerances).

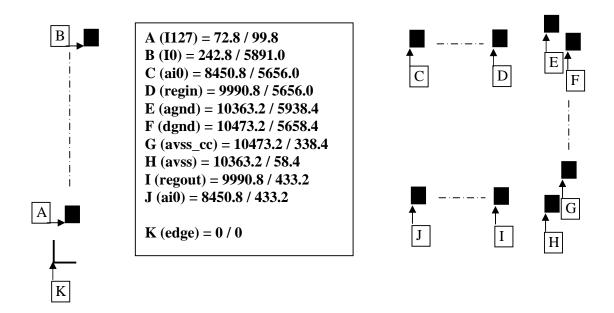

Figure 3: Definition of input pad size and pitch.

## 6 Functional description

(See the following text for more detailed information)

#### 6.1 Using VATAGP3\_1 in parallel

The VATAGP3\_1 is designed to be used in parallel for reading out a large number of channels. There are 4 bits for the chip address, giving a maximum of 16 chips on the same bus, with a total of 2048 channels. The pads are placed so that signals that go from one chip to the next are on the opposite side, making the PCB routing easy. The signals should be connected this way: (chip number in parenthesis)

vo(1) to vi(2) vob(1) to vib(2) shift\_out\_u(1) to shift\_in\_u(0) shift\_out\_d(1) to shift\_in\_d(2) regout(1) to regin(2)

All other control signals shall be in parallel.

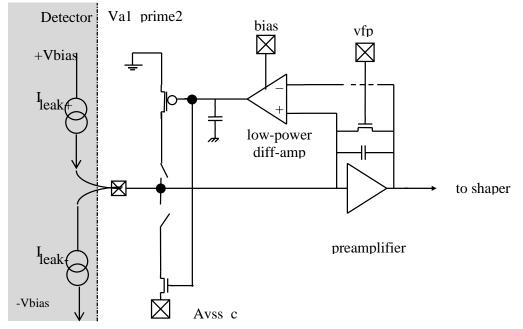

#### 6.2 Current compensation

VATAGP3\_1 uses an active current compensation by introducing a MOS source/sink at the preamplifier's input. The MOS device is controlled by a slow differential amplifier, which senses the voltage difference between the input and the output nodes of the preamp. The control signal *nside* can be used to set the current compensation to *source-* or *sink-*modus depending on which side of the detector the leakage current originates. The figure below shows the concept of this scheme.

Simplified schematic showing the principle of the current compensation used in the *Va3Tta*. The switches are controlled by *nside*. There is also a separate switch controlled by the bit *cc\_on* for turning the current compensation off (not shown).

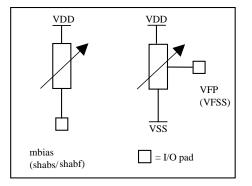

#### 6.3 Biasing

The VATAGP3\_1 is designed to have only one external bias: *mbias*. All other biases are internally generated, where most biases are a fraction of *mbias*. However, sometimes it is necessary to adjust or force the biases to other values than the nominal. Pads are available for all biases so that external adjustment is possible.

#### Generation of bias currents/voltages

Figure shows a possible approach for generating the necessary bias currents and voltages.

*mbias* is a current **into** the chip (resistor to VDD).

Figure 4: Bias current and voltage generation

#### Decoupling of power and bias lines

It is recommended to decouple the power lines to GND. Decoupling recommendations for bias lines varies, but most of the biases (including *mbias*) should be decoupled to AVSS.

Use 100 nF ceramic capacitors on the power lines as close as possible to each chip and 1-100 uF tantalum capacitors common for all chips on a PCB. Use 100 nF on the *mbias* (and eventually other biases that are externally generated) close to the chip.

#### 6.4 Control register

| <b>Bit</b> <sup>1)</sup> | Name            | Function                     |

|--------------------------|-----------------|------------------------------|

| 1                        | cc_enable       | Enable current               |

|                          |                 | compensation                 |

| 2                        | n_side          | Current compensation         |

|                          |                 | network set for connection   |

|                          |                 | to n-side of the detector.   |

| 3                        | test_on         | Test mode on                 |

| 4                        | select          | Select signal polarity       |

| 5                        | Vrcn_sel        | Selects internal bias        |

|                          |                 | generation for the Vrc bias. |

|                          |                 | Set low for positive input   |

|                          |                 | signals and high for         |

|                          |                 | negative signals.            |

| 6:9                      | addr[10:7]      | chip address                 |

| 10:137                   | Threshold       | Disable channel (assumed     |

|                          | Norm/High for   | that vthrh = $+2V/-2V$ )     |

|                          | ch[0:127]       |                              |

| 138:521                  | DAC[2:0] for    | Threshold DACs               |

|                          | ch[0:127]       |                              |

| 522:649                  | test_enable for | Enable injection of cal-     |

|                          | ch[0:127]       | pulse into channel           |

The VATAGP3\_1 has a 649 bit long control register, set by *regin* and *clkin*.

1) Bit number in the control register. Bit 1 is the first bit after *regin*, bit 649 is the last bit before *regout*. Reverse the order when downloading the bit-stream (download bit 649 first and bit 1 last).

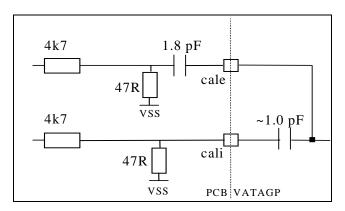

#### 6.5 ASIC test and calibration

Each channel can be individually tested. This function is enabled by setting bit *test\_on* in the control register to "1". The *test\_enable* mask must have one of it's bits set to "1" which will select the corresponding channel (selecting more than one channel is possible due to AC coupling on the inputs but is not expected to be very useful). The channel(s) that has been selected will be sensitive to test-signals injected at the *cale/cali* inputs.

Connect **either** the *cali* **or** the *cale* signal. When using the *cale* signal, place the 1.8 pF capacitor very close to the chip to prevent pickup. When using the *cali* signal, there is a  $\sim$ 1.0 pF capacitor internally in the chip.

A voltage step of 10 mV on the 1.8 pF capacitor gives an input signal charge of 18 fC (~5 MIP).

#### 6.6 Threshold DACs

The DACs have nominally 3 mV step size. The step size can be changed by forcing a different *ref\_bi*. The step size in [mV] is **ref\_bias**[ $\mu$ **A**]\***0.15**.

| DAC0 | DAC1 | DAC2 | Threshold adjust<br>(ref_bias = $20\mu A$ ) |

|------|------|------|---------------------------------------------|

| 0    | 0    | 0    | 0 mV                                        |

| 0    | 0    | 1    | -3 mV                                       |

| 0    | 1    | 0    | -6 mV                                       |

| 0    | 1    | 1    | -9 mV                                       |

| 1    | 0    | 0    | 0 mV                                        |

| 1    | 0    | 1    | 3 mV                                        |

| 1    | 1    | 0    | 6 mV                                        |

| 1    | 1    | 1    | 9 mV                                        |

### 7 Readout modes

The VATAGP3\_1 has three different readout modes. After the physics event, each preamplifier will integrate its eventual signal. The slow shaper will shape the signal with a shaping time of 4 us, and the fast shaper with a shaping time of 150 ns. If the signal of the fast shaper has a value larger than the external threshold (*vthr* or *vthr\_h*), a trigger on the *to/tob* and *mgo* lines occur. When the slow shaper reaches the signal peak (nominally after 4 us), the external hold signal (*sh/shb*) should be applied to sample the peak value. Immediately after this, the readout can start.

#### a) Mode 1: Serial readout

Readout is similar to the VA+TA type of ASICs from Ideas.

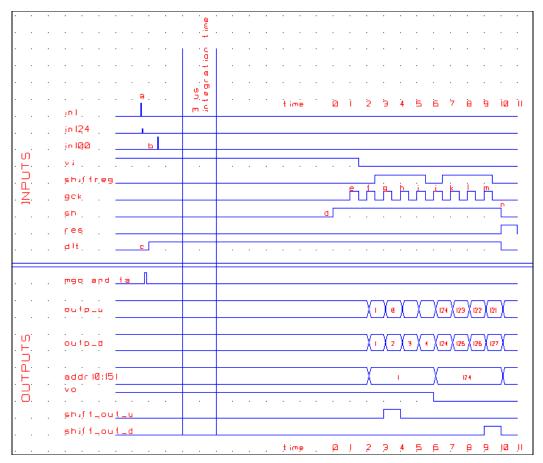

A shift-register will enable readout of one channel at a time. The readout starts with clocking one bit into the first channel of the shift-register with the *shift\_in\_d* and *gck/gckb* signals. See Figure 4 for an example of the timing in this mode. The logic part of the chip can be reset either by applying the *res/resb*, or by running through the full read-out sequence (more than 128 clocks) so that the last shift bit is clocked out of the register.

On power-up, a reset signal should be applied to reset the internal registers/latches with a pulse ( $\sim$ 1us- 1ms) on the *res/resb* lines. Eventually, a number of clocks exceeding the number of channels will set the shift-register to zero.

In this mode, the following input signals are not in use and can be left unconnected:

| shift_in_u  | (internal pull down) |

|-------------|----------------------|

| shift_out_u |                      |

| shiftreg    | (internal pull up)   |

| shiftregb   | (internal pull down) |

| vi          | (internal pull down) |

| vib         | (internal pull up)   |

| dlt         | (internal pull down) |

| dltb        | (internal pull up)   |

| VO          |                      |

| vob         |                      |

|         |                     |        | t me        | • | • | • | •    | •   | • | • | •      | • | • | •  | •    | •        | •      |     | •  |

|---------|---------------------|--------|-------------|---|---|---|------|-----|---|---|--------|---|---|----|------|----------|--------|-----|----|

|         |                     |        | ê           |   |   |   |      |     |   |   |        |   |   |    |      |          |        |     |    |

| · ·     |                     |        | τ<br>0<br>1 |   | - |   |      |     |   |   | •      |   |   | •  |      |          | -      |     | ·  |

| · ·     |                     |        | on<br>e     | · |   | • |      |     | • |   | -<br>- | 2 |   | Л  |      |          | 128    | • • |    |

| • •     |                     | a<br>M | Ē           |   | • | • | t i  | në. |   | Ø | 1      | 2 | 3 | .4 | .121 | 127      | ,120   | 129 |    |

|         | in124               |        |             |   |   |   |      |     |   |   |        |   |   |    |      |          |        |     |    |

| ហ       | jo 100              | ь      |             |   |   |   |      |     |   |   |        |   |   | _  |      |          |        |     |    |

| INPUTS  | shift_in <u>_d</u>  |        |             |   |   |   |      |     |   |   | 5      | 1 |   |    |      |          |        |     |    |

| · Z·    | gok                 |        |             |   |   |   |      |     |   |   | ₼      |   |   | _  |      |          | Ľ      |     |    |

| · ·     | sh                  |        | _           |   |   |   |      |     |   | : |        |   |   |    |      |          |        | .   |    |

|         | res                 |        |             |   |   |   |      |     |   |   |        |   |   | _  | —    |          |        | [   | 1_ |

| ່ ທ     | mgo and <u>ta</u>   |        |             |   |   |   |      |     |   |   |        |   |   | _  | -    |          |        |     |    |

| OUTPUTS | outpid              |        |             |   |   |   |      |     |   |   | ) (    |   | 2 | X  | 12   | 5 / 128  | 5 (127 | )   |    |

|         | shift <u>lout</u> d |        |             |   |   |   |      |     |   |   |        |   |   | _  |      |          |        | 1   |    |

| . Ō.    |                     |        |             |   |   |   |      |     |   |   |        |   |   |    | Ι.   |          |        |     |    |

| • •     |                     | .      |             |   |   |   | t ii | me  |   | Ø | ļ      | 2 | Э | 4  | 121  | 5<br>127 | ,128   | 129 |    |

Figure 4: Serial readout

- a) Physics events happen almost simultaneously in channel 1 and 124. Since the signal is larger than the threshold, a trigger (mgo, ta/tb) is generated. The fast shaper for the trigger logic has a shaping time of 150 ns, which means that dependent of the signal amplitude and the threshold *vthr*, the trigger can be delayed up to 150 ns.

- b) Another physics event happen some time later in channel 100. This event also generates a trigger.

- c) After 4 us, the sample-and-hold signal *sh/shb* goes high. The signal in channel 1 and 124 has reached the peak, while channel 100 has not fully reached the peak yet.

- d) A shift bit is clocked into the shift-register by *shift\_in\_d* and *gck/gckb*. The analogue value of channel 0 is enabled at *outp\_d/outm\_d*. For each clock (*gck/gckb*), the shiftbit is clocked to the next channel.

- e) The last channel is enabled. The *shift\_out\_d* goes high to give a *shift\_in* for the next chip in the chain.

- f) A reset is applied to reset the shift-register. This is not necessary if all channels have been clocked, so that the shift bit has been clocked out of the chip.

#### 7.1 Mode 2: Sparse readout

In this readout mode, only the channels with a trigger (signal above the threshold) will be read out to increase the readout speed. As in serial readout, the hold signal sh/shb must be applied 4 us after the trigger.

All channels with a trigger will get a read tag. By clocking once with the gck/gckb, the analogue value and the address of the first channel with a tag will be available on the output. After the next clock of gck/gckb, the next channel with a tag will be available. The *vo* signal goes low when all channels with triggers are read out. If the chip shall be reset before all channels are read out, apply the *res/resb* signal.

In this mode, the following input signals are not in use and can be left unconnected:

| shift_in_u  | (internal pull down) |

|-------------|----------------------|

| shift_out_u |                      |

| shift_in_d  | (internal pull down) |

| shift_out_d |                      |

These signals have a fixed level:

| vi (chip 0)  | connect to VSS (logic low)  |

|--------------|-----------------------------|

| vib (chip 0) | connect to VDD (logic high) |

| shiftreg     | connect to VSS (logic low)  |

| shiftregb    | connect to VDD (logic high) |

dlt/dltb can optionally be used. If they are not used, no connection to these pads is necessary.

|                                |                 | . e .     |   |   |      |    |          |   |              |                 |              |   |   |   |   |

|--------------------------------|-----------------|-----------|---|---|------|----|----------|---|--------------|-----------------|--------------|---|---|---|---|

|                                |                 | t ime     |   |   |      |    |          |   |              |                 |              |   |   |   |   |

|                                |                 |           |   |   |      |    |          |   |              |                 |              |   |   |   |   |

|                                | a               | ns<br>teg |   |   |      |    |          |   |              |                 |              |   |   |   |   |

| jn l                           | 1               | m .S      |   | • | t i  | me | Ø        | Ì | 2            | З               | 4            | 5 | 6 | 7 | 8 |

| 1.11                           |                 |           |   |   |      |    |          |   |              |                 |              |   |   |   |   |

|                                |                 |           |   |   |      |    |          |   |              |                 |              |   |   |   |   |

| in II<br>T O                   |                 |           |   |   |      |    |          |   |              |                 |              |   |   |   |   |

| i Ε×i                          |                 |           |   |   |      |    |          | . |              |                 |              |   |   |   | _ |

| sh.                            | fineg           |           |   |   |      |    |          |   | 4            |                 | _            |   |   |   | _ |

| О<br>Н. уі<br>П. яп.<br>Д. ясі | . <u> </u>      |           |   |   |      |    |          | Ĺ | ╧            |                 | 占            |   |   |   |   |

| sh                             |                 |           |   |   |      |    | <u> </u> |   |              |                 |              |   |   |   |   |

| re:                            | ā               |           |   |   |      |    |          |   |              |                 |              |   |   |   |   |

|                                |                 |           |   |   |      |    |          |   |              |                 |              | 5 |   |   |   |

| . <u>.</u>                     |                 |           | • | • |      |    | •        |   |              |                 |              |   |   |   |   |

|                                | et bae          |           |   |   |      |    |          |   |              |                 |              |   |   |   |   |

| jngi                           | o and <u>ta</u> |           |   |   |      |    |          |   |              |                 |              |   |   |   |   |

| ហ                              | <br>tp_d        |           |   |   | <br> |    | <br>     |   | -v-          | Υ <sub>12</sub> |              |   |   |   | _ |

| . ⊢"                           |                 |           |   |   |      |    |          |   | _^_          | _\_             | <u>_</u> /_  |   |   |   |   |

| · 🖬 · · · ·                    |                 |           |   |   |      |    |          |   | ~~           | ~~              | ~~           |   |   |   |   |

|                                | tr (0+15)       |           |   |   |      |    |          |   | _ <u>\</u> _ |                 | <u>**</u> X_ |   |   |   | _ |

|                                |                 |           |   |   |      |    |          |   |              |                 |              |   |   |   | _ |

|                                |                 |           |   |   | ti   |    | Ø        |   | 2            | З               | 4            | 5 | 6 | 7 | 8 |

Figure 5: Sparse readout

- a) Physics events happen almost simultaneously in channel 1 and 124. Since the signal is larger than the threshold, a trigger (mgo, ta/tb) is generated. The fast shaper for the trigger logic has a shaping time of 150 ns, which means that dependent of the signal amplitude and the threshold, the trigger can be delayed up to 150 ns.

- b) The disable\_late\_trigger *dlt* is applied. This will discard all triggers after this moment. Another physics event happen some time later in channel 100. No trigger is given because *dlt* is high.

- c) After 4 us, the sample-and-hold signal *sh/shb* goes high. The signal in channel 1 and 124 has reached the peak and are held.

- d) The *gck/gckb* clocks once. Since veto in *vi* from the previous chip in the chain is high, no action is taken.

- e) The *gck/gckb* clocks once. Veto in *vi* is low, and the first channel with a hit is enabled at the output together with its address.

- f) The next and last channel with a hit is enabled at the output together with its address. Veto out *vo* goes low to indicate that all channels are read out and enable readout of the next chip in the chain.

- g) *Sh* and *dlt* goes low. A reset is applied to reset the shift-register by a pulse on *res/resb*. This is not necessary if all hit channels have been clocked, so that the veto out in the last chip has gone low.

#### 7.2 Mode 3: Sparse readout with neighbour channels

This mode is equal to the sparse readout, except that the neighbours of the channel(s) with trigger can also be read out.

As in serial readout, the hold signal *sh/shb* must be applied 4 us after the trigger.

All channels that trigger will get a read tag. By clocking once with the *gck/gckb* and with *shiftreg* low, the analogue value and the address of the first channel with a tag will be available on the output. By setting *shiftreg* high and clocking more clocks, the neighbours of the trigger channel will be available.

Be setting *shiftreg* low and giving another clock of *gck/gckb*, the next channel with a trigger will be available.

All channels with triggers are read out when the *vo* goes low. If the chip shall be reset before all channels are read out, apply the *res/resb* signal.

These signals have a fixed level:

| vi (chip 0)  | connect to VSS (logic low)  |

|--------------|-----------------------------|

| vib (chip 0) | connect to VDD (logic high) |

dlt/dltb can optionally be used. If they are not used, no connection to these pads is necessary.

Figure 6: Sparse readout with neighbour channels

- a) Physics events happen almost simultaneously in channel 1 and 124. Since the signal is larger than the threshold, a trigger (mgo, ta/tb) is generated. The fast shaper for the trigger logic has a shaping time of 150 ns, which means that dependent of the signal amplitude and the threshold, the trigger can be delayed up to 150 ns.

- b) The disable\_late\_trigger *dlt* is applied. This will discard all triggers after this moment.

- c) Another physics event happen some time later in channel 100. No trigger is given because *dlt* is high.

- d) After 4 us, the sample-and-hold signal *sh/shb* goes high. The signal in channel 1 and 124 has reached the peak and are held.

- e) The *gck/gckb* clocks once. Since veto in *vi* from the previous chip in the chain is high, no action is taken.

- f) The gck/gckb clocks once with *shiftreg* = low. Veto in *vi* is low, and the first channel with a hit is enabled at the output together with its address.

- g) The *gck/gckb* clocks once with *shiftreg* = high. The analogue values of the two next neighbour channels of the hit channel are read out on the *outp\_u/outm\_u* and *outp\_d/outm\_d* lines.

- h) Same as g)

- i) Same as g)

- j) The gck/gckb clocks with *shiftreg* = low. The next channel with a hit is enabled at the output together with its address.

- k) Same as g)

- 1) Same as g)

- m) Same as g)

- n) The chip is reset by setting *sh* and *dlt* low and by giving a short *res/resb* pulse. *Dlt* is not available on this ASIC.

## 7.3 Mode 4: Random Access Read-out (RAR) with neighbour channels

In this mode, any desired channel can be read out (Random Access Read-out). A typical use of the RAR mode would be a read-out that first reads all triggered channels (mode 2), or primary channels. From the address of the primary channels, one can determine the address of their neighbours. By switching to RAR mode, the neighbouring channels can be read out, e.g. to identify charge sharing or for common mode subtraction.

The hold signal *sh/shb* should be active during the read-out.

To set a particular ASIC in RAR-mode, the CS/CSB signals should be active. This enables the address input pins ai0-ai6. The channel to be read out is selected by setting the according channel address on the address input bus. This address is clocked into the ASIC by clocking once with the gck/gckb and with *shiftreg* low. The analogue value and the address of the channel will be available on the output. This sequence can be repeated to read out any desired number of channels.

By setting *shiftreg* high and *CS/CSB* low and clocking more clocks, the neighbours of the last channel read out in RAR mode will be available.

These signals have a fixed level:

| vi (chip 0)  | connect to VSS (logic low)  |

|--------------|-----------------------------|

| vib (chip 0) | connect to VDD (logic high) |

dlt/dltb can optionally be used. If they are not used, no connection to these pads are necessary.

An example read-out sequence using RAR mode and mode 2 can be:

- a. Physics events happen almost simultaneously in channel 1 and 124. Since the signal is larger than the threshold, a trigger (mgo, ta/tb) is generated. The fast shaper for the trigger logic has a shaping time of 40 ns, which means that dependent of the signal amplitude and the threshold, the trigger can be delayed up to 40 ns.

- b. The disable\_late\_trigger *dlt* is applied. This will discard all triggers after this moment.

- c. Another physics event happen some time later in channel 100. No trigger is given because *dlt* is high.

- d. After 250 ns, the sample-and-hold signal *sh/shb* goes high. The signal in channel 1 and 124 have reached the peak and are held.

- e. The *gck/gckb* clocks once. Since veto in *vi* from the previous chip in the chain is high, no action is taken.

- f. The gck/gckb clocks once with *shiftreg* = low. Veto in *vi* is low, and the first channel with a hit, channel 1, is enabled at the output together with its address.

- g. The *gck/gckb* clocks once with *cs/csb* active, and the address of channel 4 is applied to the address input buss ai0 ai6. *shiftreg* = low. The analog value of channel 4 appears on the analogue output.

- h. The *gck/gckb* clocks once with *shiftreg* = high. The analogue value of the two neighbour channels of channel 4 (channel 3 and 5) becomes available on the *outp\_u/outm\_u* and *outp\_d/outm\_d* lines.

- i. The chip is reset by setting *sh* and *dlt* low and by giving a short *res/resb* pulse.

The information in this catalogue is subject to change without prior notice.

Information given by Ideas ASA is believed to be reliable. However, no responsibility is assumed for possible inaccuracies or omission.