# Backup studies of photon detectors and read-out electronics

### Peter Križan

### University of Ljubljana and J. Stefan Institute

Aug. 9, 2004

PID upgrade meeting, KEK

Peter Križan, Ljubljana

### Motivation

**Photodetector back-up candidate: Burle MCP**

•Beam tests

•On-the-bench studies

**Read-out electronics back-up: VA64TAP**

Summary

## Motivation

### Neither the photon detector for the ARICH (baseline: HAPD) nor the corresponding electronics are off-the-shelf products.

### Check whether the available substitutes can be used as a backup solutions.

Photon detector back-up: Burle MCP PMT

## **BURLE MCP-PMT UPDATE**

- beam test results

- new info from BURLE

- setup for relative channel response

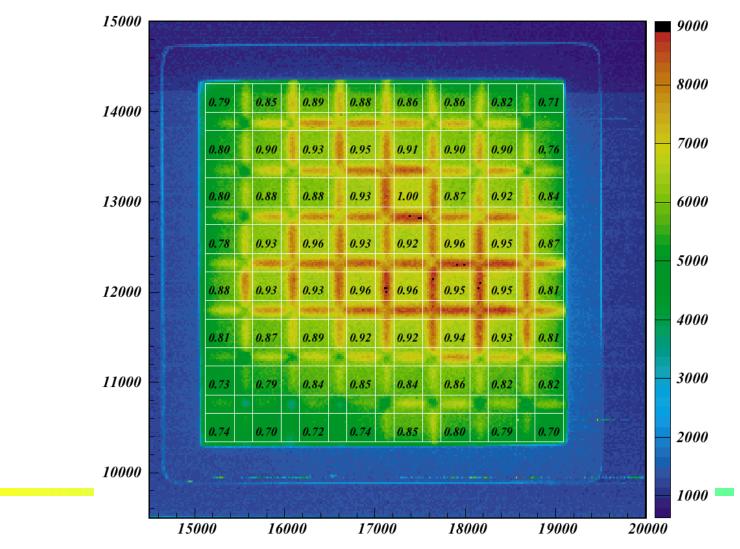

- uniformity of response

- preparation for timing measurement

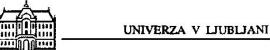

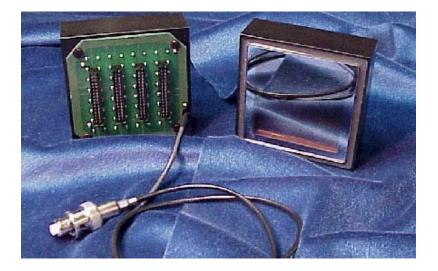

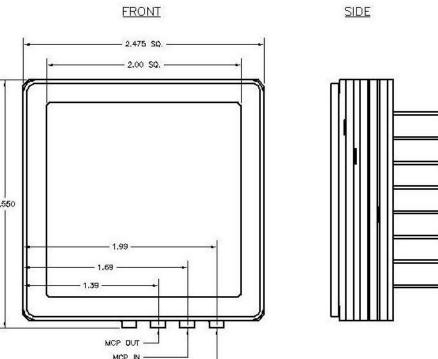

### **Data for the present version (85011)**

- PMT with three MCP steps

- box dimensions: 2.795" square

- active surface: 2" square (51%)

- 64 channels (8x8)

- pores 25 micron

- excellent timing properties

Expected improvements using  $10\mu m$  pore plates:

- better magnetic field immunity due to smaller pores and reduced gap between photocathode and MCP (successfully tested)

- collection efficiency ~ 70% (80% with additional improvements??)

They hope that by the end of summer samples will be available for testing.

They can supply unpackaged PMTs with smaller outer dimensions of the product (active aea 51% -> 63%). We would have to make our own voltage-divider network – no problem.

**NEWS FROM BURLE 2**

Burle also does some custom work and may be able to make a multiple PMT module for us – not very interesting for our tiling geometry.

Currently they are working on a new design that will increase the <sup>2.60</sup> open-area-ratio of the unpackaged PMT, but maintain the same MCP active area. No specifics yet.

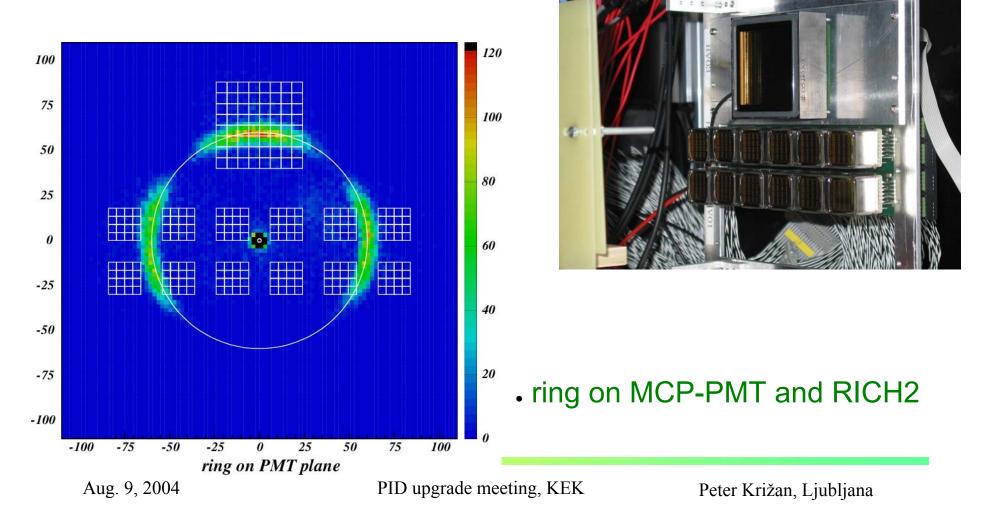

**MCP-PMT:** beam test setup

• MCP-PMT mounted together with RICH2

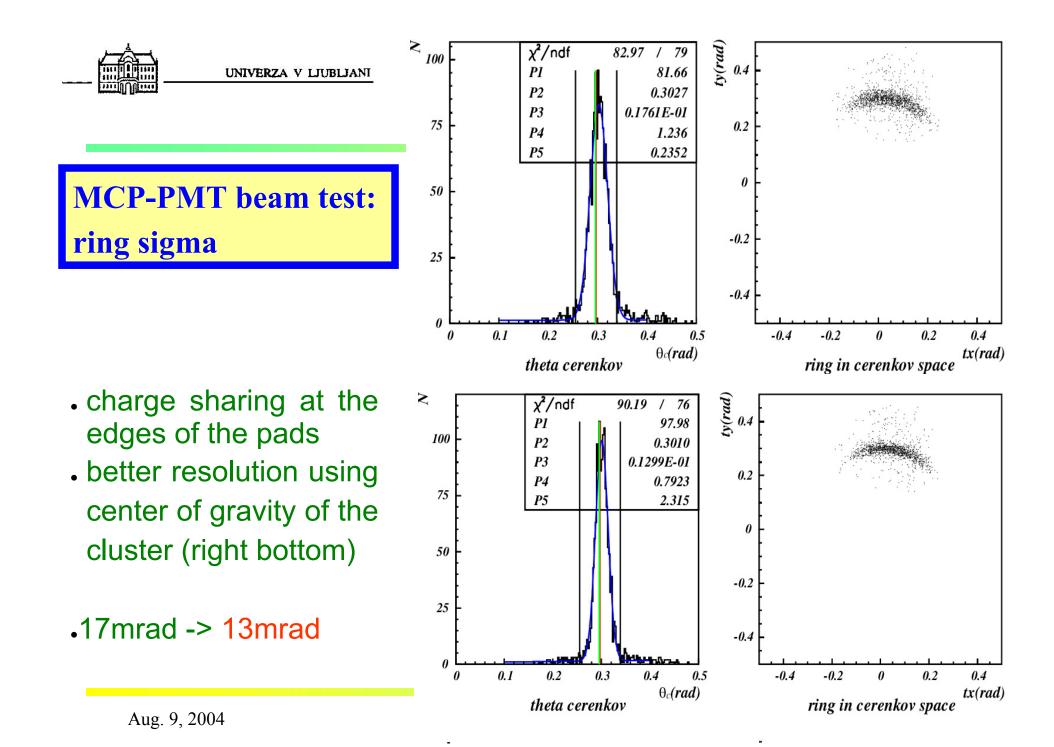

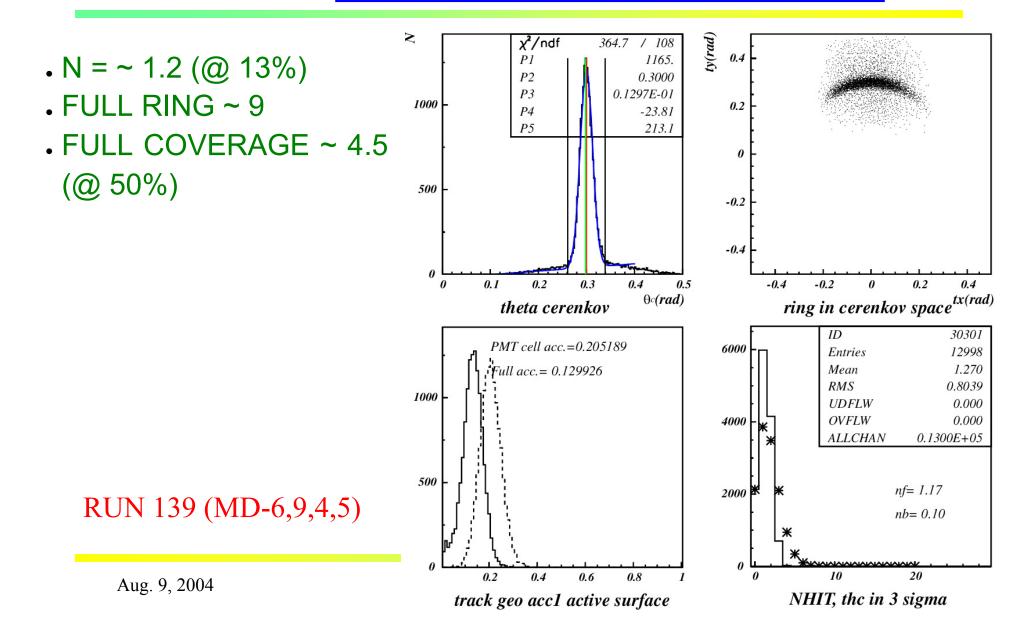

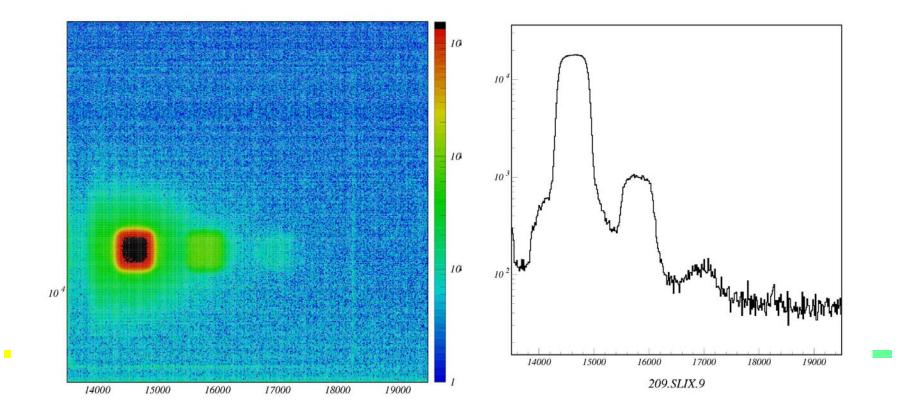

### **MCP-PMT beam test : number of hits**

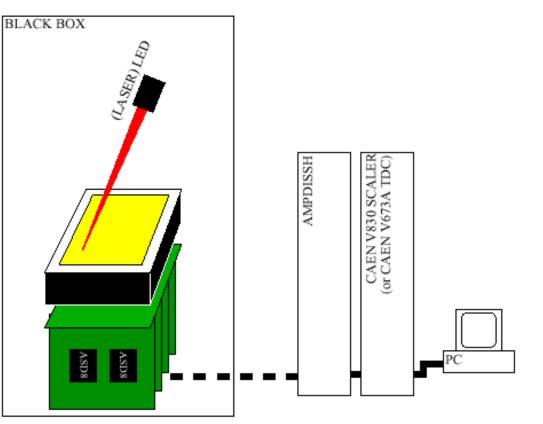

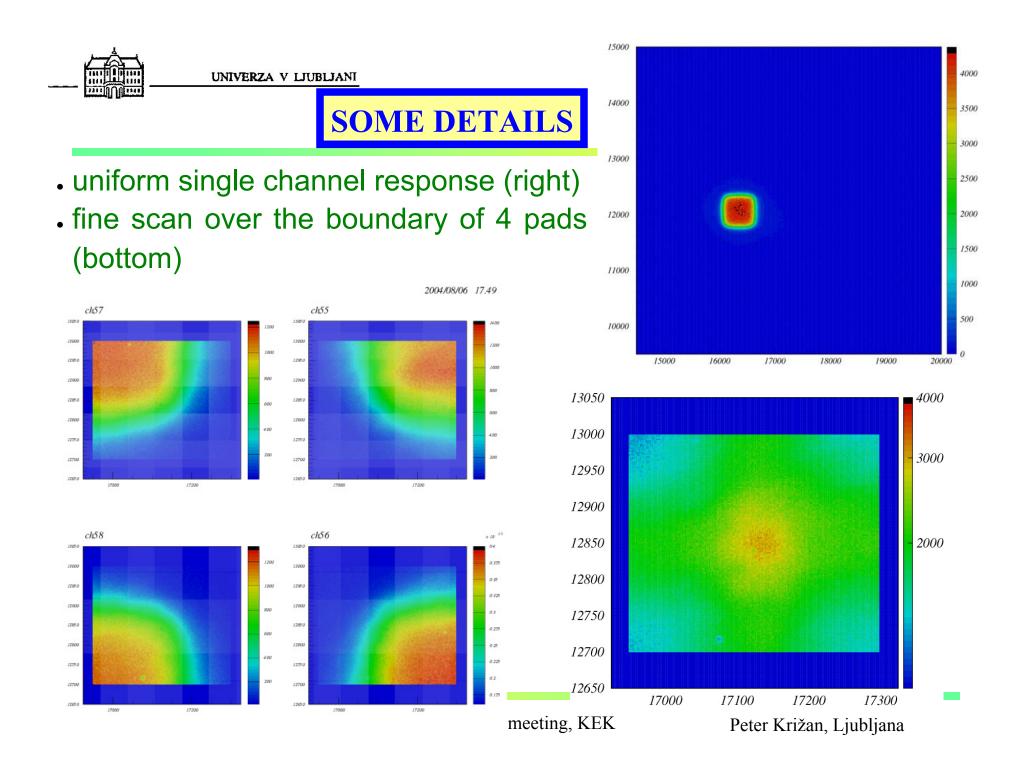

**On-the-bench tests: measurement of the surface uniformity**

Readout is based on ASD8 chips. We use 16 channel boards (two chips) developed for HERA-B outer tracker and RICH.

signal are amplified and discriminated by ASD8 boards

AMPDISSH modules are used as level adapters

digital signals are fed to VME counters

computer control by

LabWindows CVI

light source is LED focused

by microscope

#### • number of counts in the middle of the channels varies for 30%

Aug. 9, 2004

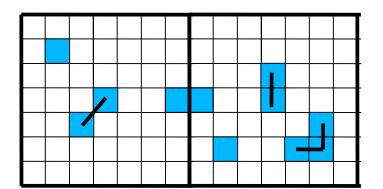

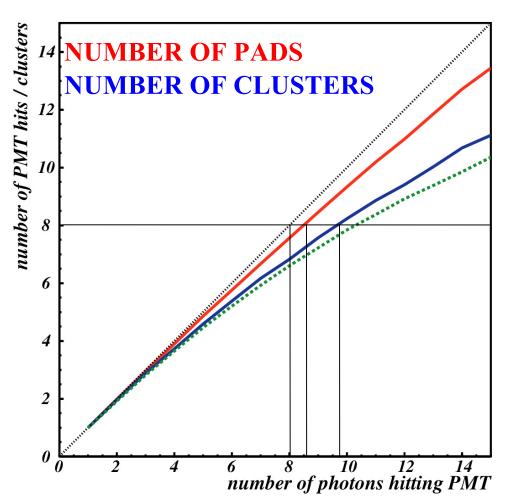

simple simulation:

- generating Cherenkov photons

- counting numer of hit pads

- counting number of clusters within the 8x8 channel areas

- 11 pads

- 7 clusters

**HITS & CLUSTERS**

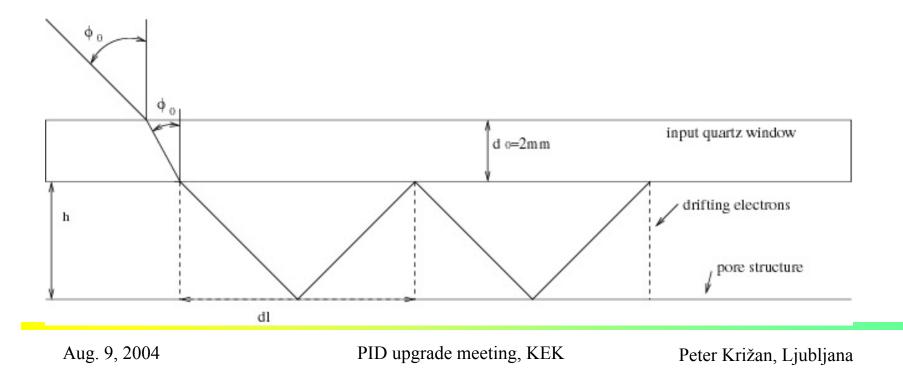

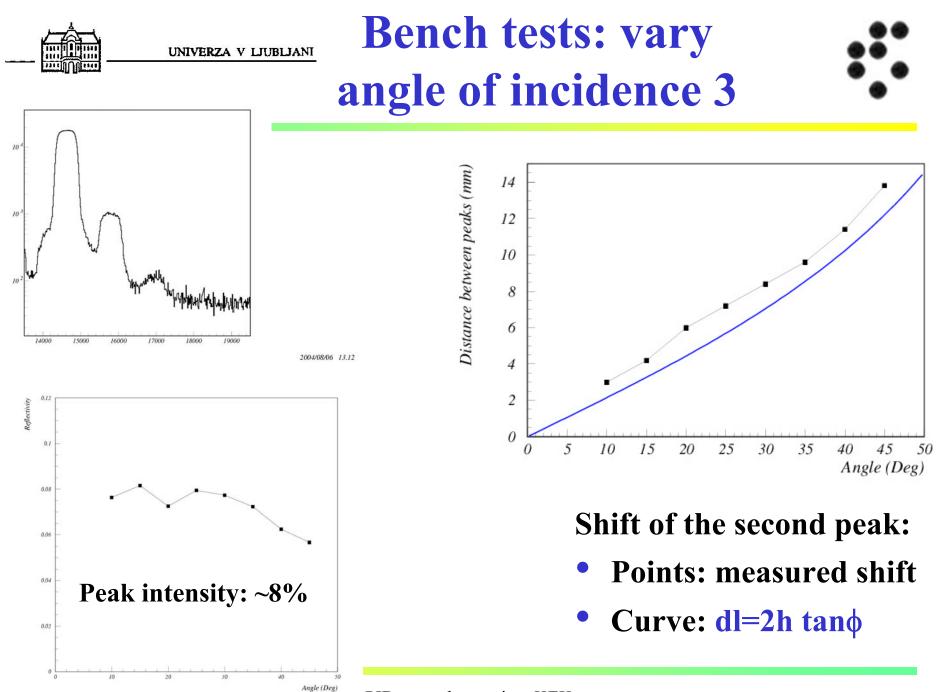

**Bench tests: vary angle of incidence**

- Photon direction 45 deg.

- Observe response of a single channel

- In addition to the single channel: displaced images

## Bench tests: vary angle of incidence 2

- Reflection on the MCP entry plane?

- In this case: spurious image should be displaced by dl=2h tan\$\$\phi\$\$=2h at 45deg: YES

PID upgrade meeting, KEK

## Bench tests: vary angle of incidence 4

Why could this be important?

- Our typical angles of incidence are quite big

- The additional 8% signal probability on the neighbour (or next-to-neighbour) pads smears the Cherenkov ring (actually it did not cause trouble in the test beam data)

- It could have impact on the timing for accurate timing applications like TOP (perpendicular incidence: 2x6mm longer photon flight = 40ps delay for reflected photons)

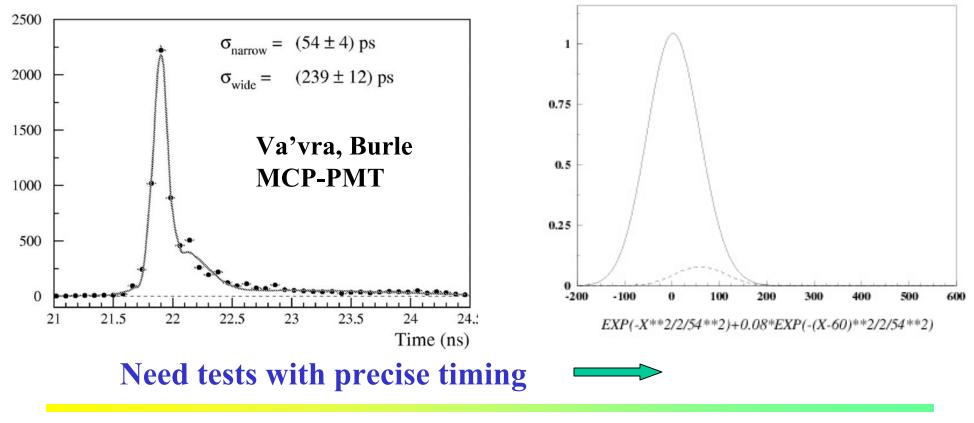

## Bench tests: time delay of the reflected photon

Can this explain the time structure observed by Jerry Va'vra?Probably not.

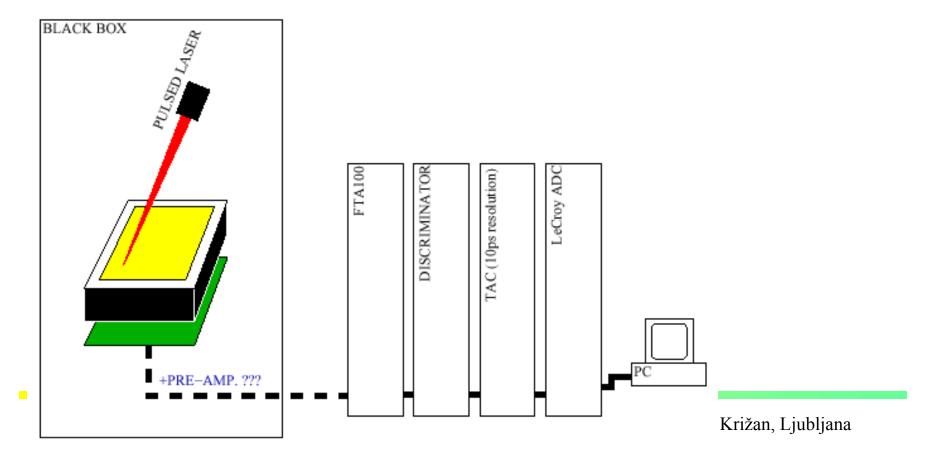

- . LED will be replaced with pulsed laser

- fast amplifier and discriminator instead of ASD8 boards

- TAC and CAMAC ADC will be used for time measurement

- **Excellent performance in beam tests**

- **Good surface uniformity**

- **Small number of photons**

- **Improvements are underway: number of photons -> ~8-9**

A very good candidate for the photon detector for both ARICH and TOP

More on-the-bench studies (timing performace) underway

Waiting for the improved model

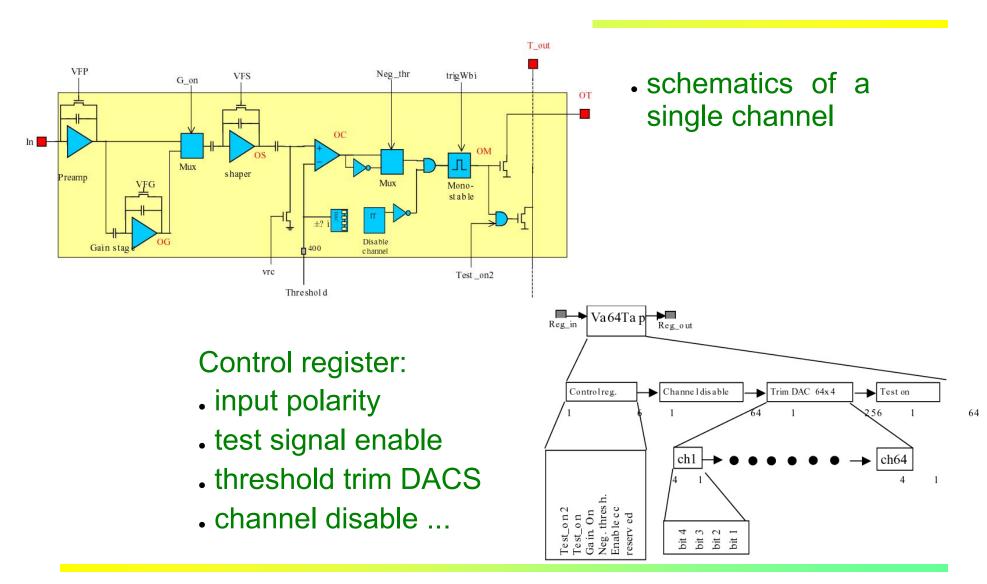

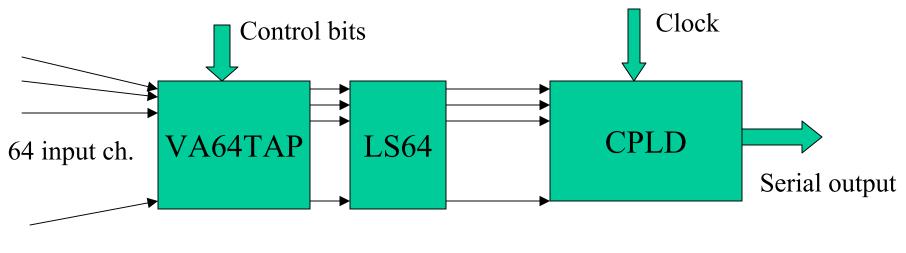

VA64TAP as readout candidate

- VA64TAP: low-power, low-noise ASIC from *ideas*

- . LS64: level adapter

VA64TAP is low-power, low-noise ASIC with 64 channels, each with:

- preamplifier (ENC ~ 500 @ 10 pF)

- amplifier (can be switched off)

- fast CR-RC shaper (75 ns)

- discriminator with 4-bit trim-DAC

- threshold uniformity: +-200e-

- threshold nominal value: 3000e-

- power: 2.3 mW/ch.

- parallel output

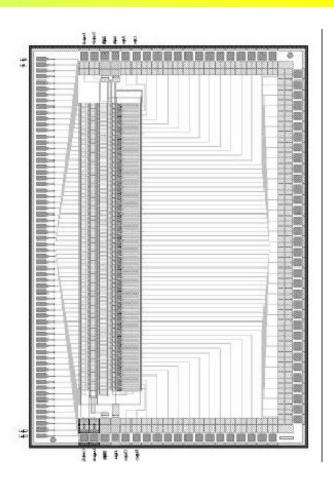

#### die size: 5.5mm x 5.4mm

PID upgrade meeting, KEK

Auxiliary chip: logic level adapter, converts current logic (from VA64TAP) into CMOS logic (0V, 2.5V - 5V)

- die size: 5.5mm x 5.4mm

- same lateral dimensions, direct channel to channel bonding

- should be mounted next to VA64TAP

The test version should as simple as possible

- VA64TAP bonded to LS64

- line for control bits

- a CPLD with external clock for 64 parallel to 1 serial conversion

- steering through a VME I/O unit

Since this is the back-up solution, the highest priority will be to make the board for the baseline electronics.

However, some activities can be done in parallel, so the plan is to

design a hybrid for the two chips and a CPLD, with input/output lines

- . design an interface (signal routing) board to the detector

- board production (2 weeks)

- mount components, bond VA64TAP to LS64

- goal: have a tested board by end of October

HAPD baseline read-out board: status, plans

Board for the baseline electronics:

- . with two read-out chips

- communication with the digital control board

- connection through an interface board (signal routing) to HAPD

Status+plan

- board being designed, finish this week

- production 2 weeks ready end of August

- then test, next iteration could be ready by end of Sept.

- •Burle MCP PMT looks like a good back-up candidate

- •Number of photons is at the moment too small, but with the improvements underway we can expect that the detector could be usefully applied

- •VA64TAP will be tested as the read-out candidate in the next few months